Hi Cadence Support

Is there a way to set a custom via as the default via?

What I am currently doing:

1. On vxl invoke 'Create via"

2. Choose via definition

3. Adjust rows, columns & cut size spacing to desired value.

4. Save then repeat doing this on each layout view.

Is there a built in feature on vxl to do this faster?

Do I need to load some skill files?

How to set a custom via as default via on VXL/GXL?

Liberate: Passive Power Calculation

I am characterizing some standard cells (NAND, NOR and D Flip-Flop) using cadence liberate (15.1.4). I am using custom Verilog-A models of the transistor. The characterization is successful with accurate delay and leakage power values bit I couldn't understand how passive power is getting calculated. I have following questions that

- Why passive power is in nJ? I believe the tool is integrating the power (for the certain input conditions of the standard cell) over the simulation time. Then essentially passive power is energy ?

- Why passive power is simulation time dependent? For example, I have run characterization for two different simulation time values (simulation time is set in the characterization tcl script) and in both cases the passive power was different while delay and leakage power is same. The change in passive power would also change the dynamic power results in the synthesis tool. How to select this simulation time?

Regards,

Farhan

How to save subckt parameters in Spectre

I have device model in subckt form with instance parameter "w".

This model has another parameter "r" which is a function of "w".

How to save subckt parameter "r" as I sweep parameter "w" in Spectre.

Thanks,

How to create a BJT symbol in 65nm?

How do I send Stability Summary into the Calculator?

Hello,

I have an iprobe in a loop of a feedback amplifier, and I am running PSS with PSTB simulation. When simulation finishes, I click on ADE L results >> Analysis "pstb" >> Function "Stability Summary", and this shows me the Phase Margin and Gain Margin summary.

How do I load these results into a calculator to send them to ADE? I need this because I want to run Monte Carlo on my amplifier to check that it will be stable with process/mismatches.

I am using the following versions:

MMSIM Version: 13.1.1.660.isr18

Virtuoso Version: IC6.1.8-64b.500.1

irun Version: 14.10-s039

Spectre Version: 18.1.0.421.isr9

Many thanks in advance!

Hspice replacement for Switch from AnalogLib

Hello ,

I was using switch component from AnalogLib in Spectre (open voltage=0, closed voltage =1 , Open Switch Resistance=1G and Close switch resistance = 1) and I have recently developing a test circuit in Hspice . Is there any component or subcircuit /macro model in hspice which can replace switch I used in spectre . I tried VCRES but it does not seems to work.

Any help will be really appreciated .

Thanks

stimulus test bench

hello sir, sir when I test my circuit in test bench how I can decide the size of two cascaded inverter size that is best of my circuit. Is there any method to decide the size of inverters? please help me. I am attaching the image of test bench.

ADE Assembler - Changing the Maximum Jobs while a Run is In Progress

I am using ADE Assembler in IC617.

I was wondering if there is a way to change the Maximum Jobs entry in the Job Policy Setup form, during an active run?

I tried updating the parameter during the run, but only when I stop and restart it do the changes come into effect.

I would like to manually manage the Maximum Jobs during a run as resources come and go.

I am using a local distribution method.

ADE L simulation gave error!

Dear All,

I am a new on Cadence Virtuoso, I followed one tutorial and done exactly the same but when I tried to simulate I got following error!

generate netlist...

Begin Incremental Netlisting Nov 18 14:19:20 2019

ERROR (OSSHNL-116): Unable to descend into any of the views defined in the view list, 'spectre cmos_sch cmos.sch schematic veriloga', for the

instance 'MN1' in cell 'inverter100'. Add one of these views to the cell 'nmos' in the

library 'IC-gpdk', or modify the view list so that it contains an existing view.

End netlisting Nov 18 14:19:20 2019

ERROR (OSSHNL-514): Netlist generation failed because of the errors reported above. The netlist might not have been generated at all, or the generated netlist could be corrupt. Fix the reported errors and regenerate the netlist.

...unsuccessful.

I tied to setup-> environment but then what should I include?

Also tried setup->model library

My design is a simple schematic inverter, I used IC-gpdk technology !

check and save shows no error

INFO (SCH-1170): Extracting "inverter100 schematic"

INFO (SCH-1426): Schematic check completed with no errors.

INFO (SCH-1181): "TEST100 inverter100 schematic" saved.

Regards

Cadence Calibre LVS Error with missing connection.

Hi,

I got this error in my LVS report. My layout and my schematic both connect good, however the report shows missing connection in my Source Netlist. I wondering where is the Source Netlist circuit from? How to solve this problem?

Thanks!

Spectre assert output message - printing a variable

Hello,

Is it possible in spectre assert statement to print in the warning message a parameter or a variable?

For exmaple something like this

pmos_vgs assert mod=pch expr="(abs(V(g,s))>1.3)" message="Maximum gate source voltage exceeded the limit %d",abs(V(g,s))) duration=0.1n

I know the message doesn't work but is there something like this?

Thanks

Sherif

Error during ADE spectre simulation

Hello,

I am facing the problem below after running the simulation from ADE spectre, I made simple CMOS inverter to demonstrate you this error. It looks like ADE is not able to read the model file, I am using the ams 0.35 um technology.

My cadence version is IC6.1.5 64 bit

Error found by spectre in `Test_bench_1':`I0', during hierarchy flattening. ERROR (SFE-2001): "/home/opt/ams410/c35/cmos53.scs" 29: `I0.MN0': Problem in evaluating conditional expression for instantiation: Unknown parameter name `modn' found in expression. ERROR (SFE-2001): "/home/opt/ams410/c35/cmos53.scs" 593: `I0.MP0': Problem in evaluating conditional expression for instantiation: Unknown parameter name `modp' found in expression. Error found by spectre in `modn':`I0.MN0', in `Test_bench_1':`I0', during hierarchy flattening. ERROR (SFE-1997): "/home/opt/ams410/c35/cmos53.scs" 33: I0.MN0.notvalid: parameter `errorif': Unknown parameter name `modn' found in expression. Error found by spectre in `modp':`I0.MP0', in `Test_bench_1':`I0', during hierarchy flattening. ERROR (SFE-1997): "/home/opt/ams410/c35/cmos53.scs" 597: I0.MP0.notvalid: parameter `errorif': Unknown parameter name `modp' found in expression. -- |

Does saving more number of nets increase simulation time

Hi All,

What is the impact on simulation time with number of nets saved ?

Thanks & Regards,

Prasad

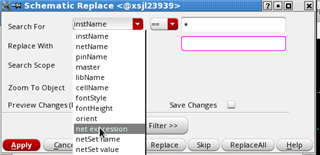

Renaming multiple wires using wildcard

Hi,

Is there way to rename multiple signals using regular expression.

e.g i many have 50 signals with _0 in the name. I want to rename it _1 either using GUI or script.

I tried using "net expression" in Schematic Replace menu but it didn't work. May be I wasn't giving query correctly. I was typing *0* in search for and "*1*" in replace with section.

Thanks

Small signal analysis during transient, triggered by event

I know about how to run things like ac, stb, and info and set times during transient analysis, but is it possible to run one of these, say ac, at a time determined during the transient simulation itself?

For example, say I would like to run an AC sim when a particular voltage crosses 0.

Hotel Revenue Management Courses - Ehotel Management

The hotel management is consistently emerging in India from the last years and hotel management has become quite prominent as a career. We also Provide Hotel Revenue Management Courses.

The revenue department is the foremost part of the hotel and it is very difficult to manage it. So keeping this in mind, we provide Restaurant Profitability Analysis course which will assist you in how to earn better profit and how to invest earned profit. This course will offer you guidance to achieve business objectives.

Moreover, we also focus on other curricular activities like group discussion, personal interview, aptitude tests, etc that will help boost up the confidence of the aspirant.

These courses will be conducted by professionals in our organization and will cover all practical aspects of the latest trends. We aim to make you quintessential employees of your hotel. So don’t waste your time and hurry up. Join these courses at a pocket-friendly price to ameliorate your skills and get promoted.

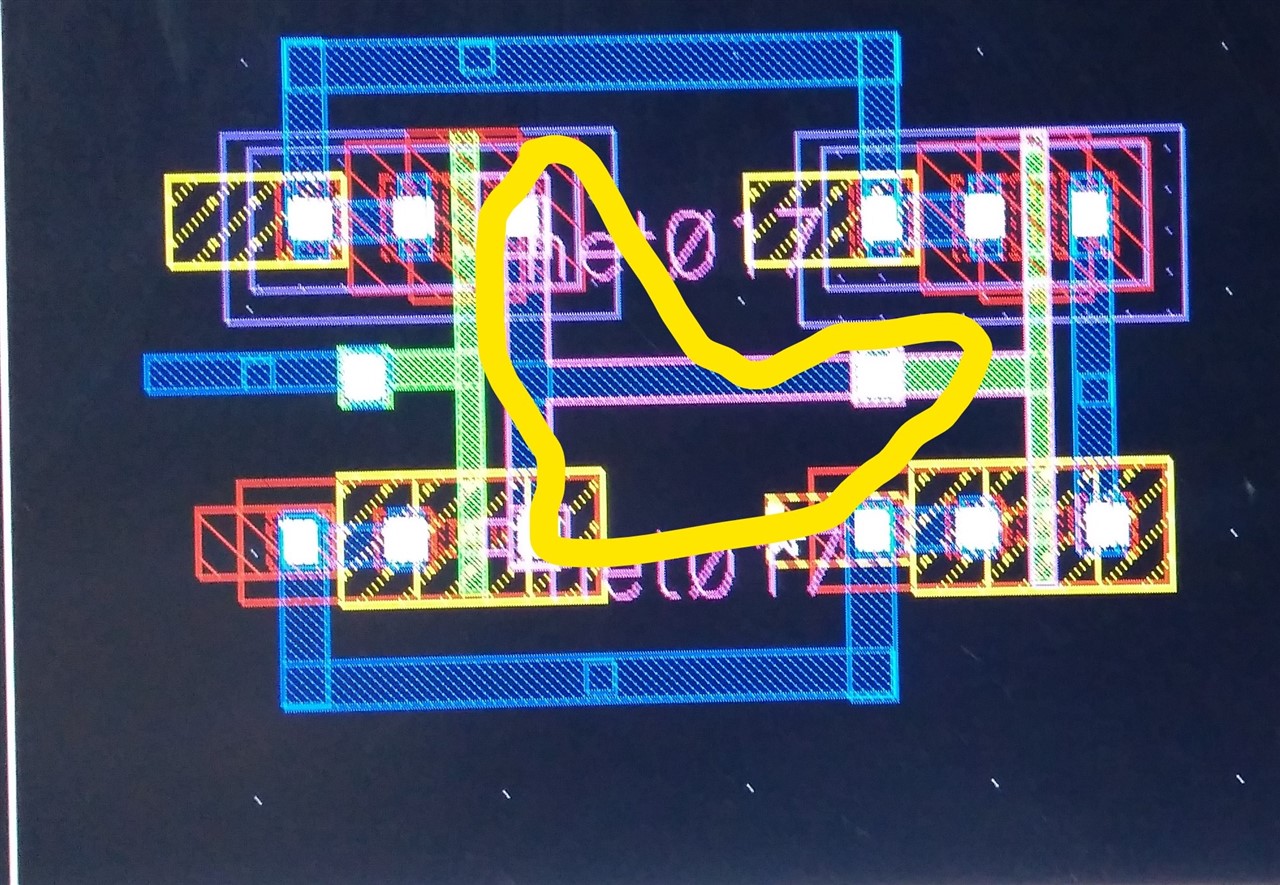

Unbound pins when running Assura LVS in Virtuoso Layout

hello sir, when i draw the layout of the buffer circuit, there is no DRC error but there is one LVS error that occurred which is related to unbound pin.i attached the image of my layout, in this image the highlighted part shows the error.

Cannot EDIF out

Hi,

I tried to edif out an inv schematic in library test which contains all devices in inv.

But edifout.log shows "Error : Failed to open library test -- exiting". However, I succeeded edif out from library analogLib.

What is the difference between test defined by me with analogLib? How can I edifout successfully?

Thanks.

malias function

Hi,

Does ADEXL has the "malias" function as in HSPICE?

Ex:

.malias nch = nch_mvt

(I want to change all 'nch_mvt' in the schematic to 'nch' without modify schematic )

thanks.

Set Subwindow ID for each Trace / Waveform

Hello,

I am working with IC 6.1.8. After a transient simulation in ADE Explorer, where I have defined several outputs (signals and expressions), all signal-waveforms are plotted in the same subwindow and all defined expressions are plotted each in a separate subwindow (although they are based on the same x-value range / time range). I would like to know if there is any possibility to define the subwindow a waveform (expression / signal) is plotted to?

It would be ok if its only possible for expressions (e.g. in the following way: "subwindow(v("/X1" "?result" "tran") 1)" for plotting the waveform in subwindow 1)...

Many thanks and best regards,

Christoph