Hi, Officers,

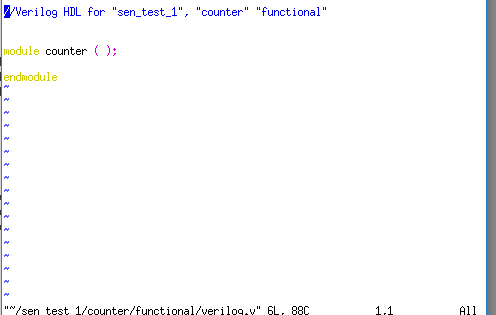

I am running the IC6.17 and after I have add the analogLib components such as

But in the input.scs, it didn't show the independent source.

// Design view name: schematic

simulator lang=spectre

global 0

// Cell name: abc

// View name: schematic

R0 (net2 0) resistor r=1K

simulatorOptions options reltol=1e-3 vabstol=1e-6 iabstol=1e-12 temp=27 \

tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \

digits=5 cols=80 pivrel=1e-3 sensfile="../psf/sens.output" \

checklimitdest=psf

tran tran stop=1n write="spectre.ic" writefinal="spectre.fc" \

annotate=status maxiters=5

finalTimeOP info what=oppoint where=rawfile

modelParameter info what=models where=rawfile

element info what=inst where=rawfile

outputParameter info what=output where=rawfile

designParamVals info what=parameters where=rawfile

primitives info what=primitives where=rawfile

subckts info what=subckts where=rawfile

saveOptions options save=allpub

Could anyone help me with it ?

Thanks a lot.

Your help appreciated.

Your help appreciated.