I need to generate multiple clocks with different delay.

So, my plan is creating a single delay module and instantiate it using for loop which apply different delay then a single clock will drive all of them.

But I still cannot make it work.

From Ken Kundert's book, it is mentioned that genvar cannot used inside the loop structure.

Is there anything that I can try?

Here is the same code for easy copy-paste.

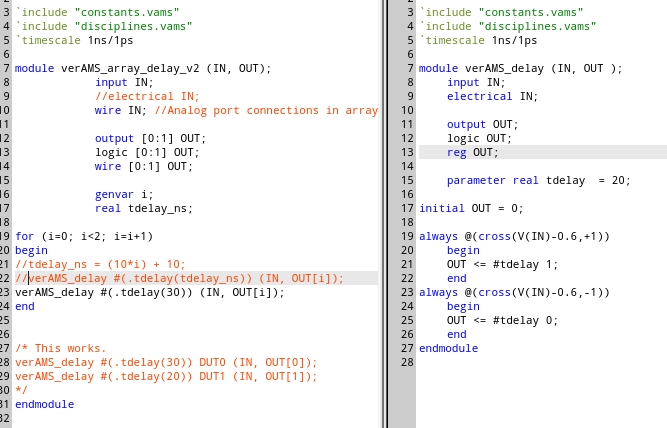

`include "constants.vams"

`include "disciplines.vams"

`timescale 1ns/1ps

module verAMS_array_delay_v2 (IN, OUT);

input IN;

//electrical IN;

wire IN; //Analog port connections in array of instances is not supported..

output [0:1] OUT;

logic [0:1] OUT;

wire [0:1] OUT;

genvar i;

real tdelay_ns;

for (i=0; i<2; i=i+1)

begin

//tdelay_ns = (10*i) + 10;

//verAMS_delay #(.tdelay(tdelay_ns)) (IN, OUT[i]);

verAMS_delay #(.tdelay(30)) (IN, OUT[i]);

end

/* This works.

verAMS_delay #(.tdelay(30)) DUT0 (IN, OUT[0]);

verAMS_delay #(.tdelay(20)) DUT1 (IN, OUT[1]);

*/

endmodule

`include "constants.vams"

`include "disciplines.vams"

`timescale 1ns/1ps

module verAMS_delay (IN, OUT );

input IN;

electrical IN;

output OUT;

logic OUT;

reg OUT;

parameter real tdelay = 20;

initial OUT = 0;

always @(cross(V(IN)-0.6,+1))

begin

OUT <= #tdelay 1;

end

always @(cross(V(IN)-0.6,-1))

begin

OUT <= #tdelay 0;

end

endmodule