Hi,

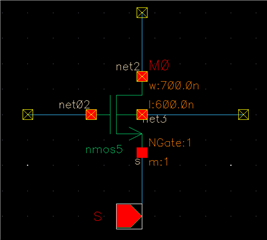

I am using 6.1.6 to do some design and I try to use some VerilogA blocks, for example the blocks in ahdlLib and some customized blocks, in my simulation. But it meets an error showing below. The error index number is ' ERROR (VACOMP-1008)'. It seams that cadence cannot compile the ahdlcmi module library. I have no idea what is that. I highlight the error message with red. Thank you very much if anyone can help me.

Simulating `input.scs' on sahand at 9:56:19 AM, Thur Jul 16, 2020 (process id: 2391).

Current working directory: /home/home2/students/haolinco/simulation/test_veriloga/spectre/schematic/netlist

Command line:

/opt/cadence/MMSIM141/tools.lnx86/bin/spectre -64 input.scs \

+escchars +log ../psf/spectre.out +inter=mpsc \

+mpssession=spectre0_53396_1 -format psfxl -raw ../psf \

+lqtimeout 900 -maxw 5 -maxn 5

spectre pid = 2391

Loading /opt/cadence/MMSIM141/tools.lnx86/cmi/lib/64bit/5.0/libinfineon_sh.so ...

Loading /opt/cadence/MMSIM141/tools.lnx86/cmi/lib/64bit/5.0/libphilips_o_sh.so ...

Loading /opt/cadence/MMSIM141/tools.lnx86/cmi/lib/64bit/5.0/libphilips_sh.so ...

Loading /opt/cadence/MMSIM141/tools.lnx86/cmi/lib/64bit/5.0/libsparam_sh.so ...

Loading /opt/cadence/MMSIM141/tools.lnx86/cmi/lib/64bit/5.0/libstmodels_sh.so ...

Reading file: /home/home2/students/haolinco/simulation/test_veriloga/spectre/schematic/netlist/input.scs

Reading file: /opt/cadence/MMSIM141/tools.lnx86/spectre/etc/configs/spectre.cfg

Reading link: /opt/cadence/IC616/tools/dfII/samples/artist/ahdlLib/and_gate/veriloga/veriloga.va

Reading link: /opt/cadence/IC616/tools

Reading file: /opt/cadence/IC616/tools.lnx86/dfII/samples/artist/spectreHDL/Verilog-A/logic/and_gate.va

Reading link: /opt/cadence/MMSIM141/tools.lnx86/spectre/etc/ahdl/discipline.h

Reading file: /opt/cadence/MMSIM141/tools.lnx86/spectre/etc/ahdl/disciplines.vams

Reading link: /opt/cadence/MMSIM141/tools.lnx86/spectre/etc/ahdl/constants.h

Reading file: /opt/cadence/MMSIM141/tools.lnx86/spectre/etc/ahdl/constants.vams

Warning from spectre during AHDL read-in.

WARNING (VACOMP-2265): "$finish;<<--? "

"/opt/cadence/IC616/tools/dfII/samples/artist/ahdlLib/and_gate/veriloga/veriloga.va", line 49: In Cadence Verilog-A, the $finish function always behaves as though the message level value is 0, regardless of the value you specify: The simulator does not report simulation time, location, or statistics about memory and CPU time usage.

Time for NDB Parsing: CPU = 94.71 ms, elapsed = 614.42 ms.

Time accumulated: CPU = 148.894 ms, elapsed = 614.434 ms.

Peak resident memory used = 66.4 Mbytes.

Warning from spectre during AHDL read-in.

WARNING (VACOMP-2265): "$finish;<<--? "

"/opt/cadence/IC616/tools/dfII/samples/artist/ahdlLib/and_gate/veriloga/veriloga.va", line 49: In Cadence Verilog-A, the $finish function always behaves as though the message level value is 0, regardless of the value you specify: The simulator does not report simulation time, location, or statistics about memory and CPU time usage.

Created directory input.ahdlSimDB/ (775)

Created directory input.ahdlSimDB//3712_artist_ahdlLib_and_gate_veriloga_veriloga.va.and_gate.ahdlcmi/ (775)

Created directory input.ahdlSimDB//3712_artist_ahdlLib_and_gate_veriloga_veriloga.va.and_gate.ahdlcmi/Linux-64/ (775)

Compiling ahdlcmi module library.

Warning from spectre during AHDL read-in.

WARNING (VACOMP-2397): Compilation failed when using pipe build. Bytecode flow will be used for encrypted VerilogA, and normal file compilation will be used for unencrypted VerilogA.

Compiling ahdlcmi module library.

Error found by spectre during AHDL read-in.

ERROR (VACOMP-1008): Cannot compile ahdlcmi module library. Check the log file input.ahdlSimDB//3712_artist_ahdlLib_and_gate_veriloga_veriloga.va.and_gate.ahdlcmi/Linux-64/../ahdlcmi.out for details. If the compiler ran out of memory, use 'setenv CDS_CMI_COMPLEVEL 0', and try again. Otherwise, contact your Cadence Customer Support representative with the netlist, log files, behavioral model files, and any other information that can help identify the problem.

ERROR (SFE-91): Error when elaborating the instance and_gate. Simulation should be terminated.

Time for Elaboration: CPU = 64.186 ms, elapsed = 9.7813 s.

Time accumulated: CPU = 213.243 ms, elapsed = 10.3959 s.

Peak resident memory used = 75.2 Mbytes.

Aggregate audit (9:56:30 AM, Thur Jul 16, 2020):

Time used: CPU = 214 ms, elapsed = 10.4 s, util. = 2.05%.

Time spent in licensing: elapsed = 129 ms.

Peak memory used = 75.2 Mbytes.

Simulation started at: 9:56:19 AM, Thur Jul 16, 2020, ended at: 9:56:30 AM, Thur Jul 16, 2020, with elapsed time (wall clock): 10.4 s.

spectre completes with 2 errors, 3 warnings, and 0 notices.

spectre terminated prematurely due to fatal error.

![]()