Our soi DeCap with 5 terminals (VBGP/VBGN is the 5th terminal) share the same power template with standard cells, however, the leakage for DeCap is 0 value while standard cells get leakage power like 0.22345. Could you please help me find where the problem might be and how could I fix it?

Our lib goes like this:

cell (DCAP4_liberate) {

area : 0;

cell_leakage_power : 0;

pg_pin (GND) {

pg_type : primary_ground;

voltage_name : "GND";

}

pg_pin (VDD) {

pg_type : primary_power;

voltage_name : "VDD";

}

leakage_power () {

value : 0;

related_pg_pin : VDD;

}

}

Our char.tcl goes like:

set_operating_condition -voltage 1.8 -temp 25

set_var extsim_exclusive 0

define_leafcell \

-type pmos_soi \

-pin_position { 0 1 2 3 4 } \

ph

define_leafcell \

-type nmos_soi \

-pin_position { 0 1 2 3 4 } \

nh

source ${rundir}/TEMPLATE/template180_dcap.tcl

set_var extsim_model_include ${rundir}/MODELS/include_models180.sp

foreach cell $cells {

lappend spicefiles /my_liberate/NETLIST/${cell}.pex.netlist

}

read_spice $spicefiles

char_library -extsim spectre -ccs -ecsm -cells ${cells}

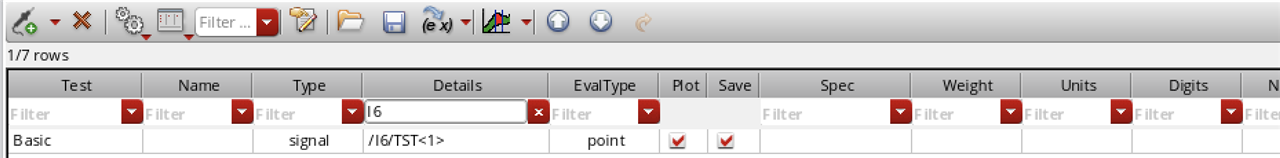

template180_dcap.tcl goes like:

set_var def_arc_msg_level 0

set_var process_match_pins_to_ports 1

set_vdd -no_model VBGP 1.8

set_vdd -no_model VBGN 0

set_var pin_based_power 0

define_template -type power \

-index_1 {0.0317486 0.0677575 0.144607 0.308619 0.658652 1.40569 3}\

-index_2 {0.0210989 0.049137 0.114435 0.266506 0.620664 1.44546 3.36632}\

power_template_7x7

set cells {\

DCAP4_liberate\

}

if {[ALAPI_active_cell "DCAP4_liberate"]} {

define_cell \

-power power_template_7x7 \

DCAP4_liberate

}