Hi all,

I want to simulate a multiplier design with verilog testbench but I am facing with this error:

```

ERROR (ADE-3076): Errors encountered while executing verilog. Unable to read Status file.

```

```

Verilog/spectre Mixed-Signal Interface 2.0

Message! Stable DC solution not found within 0

iterations. Using last calculated state to start

transient analysis. See Artist Mixed-Signal

Simulation Help for more info on obtaining an

initial solution. [Mixed_Sig]

"IE.verimix", 5: $vmx_initialize("spectre",

dc_mode_flag);

Error! List of message(s) that are acceptable now:

$do_dc

$done_dc

$switch_to_interactive

Invalid message introducer '$send_events',

unrecognized. [Mixed_Sig-VMXIMI]

"IE.verimix", 5: ...

Error! Invalid message introducer '0', expect DONE_DC

message. [Mixed_Sig-VMXIMI]

"IE.verimix", 5: $vmx_initialize("spectre",

dc_mode_flag);

Verilog/spectre Interface: 42 messages sent, 43 messages received.

2 errors

```

I searched a little bit and find this old similar questions:

Tried ams instead of spectreVerilog and it didn't resolve.

Tried to ramp up VDD to 10 Volt instead of 5 Volt and the simulation done without errors but Verilog display output for circuit's outputs is 0. (This cannot because of the circuit right? Even if I am mistaken in the schematic, it cannot be all zero for several inputs. I also tried different parameters in Verimix.)

So it seems there is no problem for analog simulations but I failed at verilog simulations and any help will be appreciated.

Thanks,

Seyyid

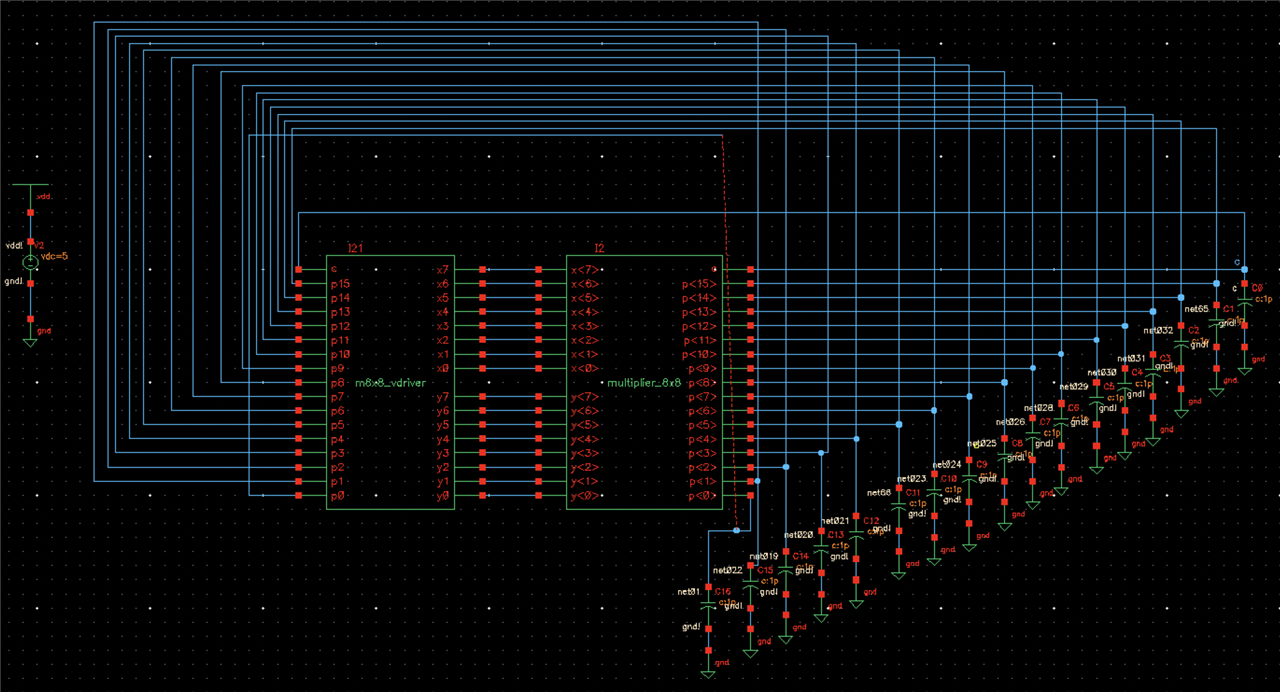

Verilog testbench schematic (with spectreVerilog config):

Verilog testbench code (I didn't use multiple bit declarations because I also suffered from bus'es in the testbench schematic):

```

//Verilog HDL for "proje", "multiplier_8x8_tb_vdriver" "functional"

`timescale 10us/1us

module multiplier_8x8_tb_vdriver ( c, p15, p14, p13, p12, p11, p10, p9, p8, p7, p6, p5, p4, p3, p2, p1, p0, x7, x6, x5, x4, x3, x2, x1, x0, y7, y6, y5, y4, y3, y2, y1, y0 );

input c, p15, p14, p13, p12, p11, p10, p9, p8, p7, p6, p5, p4, p3, p2, p1, p0;

output x7, x6, x5, x4, x3, x2, x1, x0, y7, y6, y5, y4, y3, y2, y1, y0;

reg x7, x6, x5, x4, x3, x2, x1, x0, y7, y6, y5, y4, y3, y2, y1, y0;

initial begin

x7=1'b0; x6=1'b0; x5=1'b0; x4=1'b1; x3=1'b0; x2=1'b0; x1=1'b0; x0=1'b1;

y7=1'b0; y6=1'b0; y5=1'b0; y4=1'b1; y3=1'b0; y2=1'b0; y1=1'b0; y0=1'b1;

#1; $display("x:%d * y:%d --> %d", {x7, x6, x5, x4, x3, x2, x1, x0}, {y7, y6, y5, y4, y3, y2, y1, y0}, {c, p15, p14, p13, p12, p11, p10, p9, p8, p7, p6, p5, p4, p3, p2, p1, p0});

end

endmodule

```